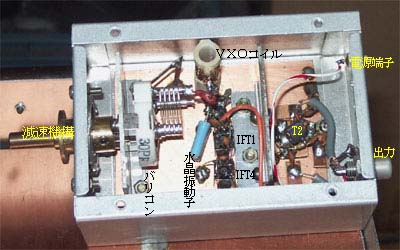

VXO用のコイルL1は10mm径のボビンを探して使いました、コアは使いません。

7kボビンを使うときは40回巻で試してください。

回路図にはありませんが、電源は貫通コンデンサを使用して供給しています。

トランシーバのメインVFOです。PLLと組み合わせて、7MHz/21MHz信号を中間周波数(11.275MHz)に変換する時の送受信周波数を可変するための発振器です。安定度を重視しVXOを採用し、可変範囲も29MHz台で100kHzとします。

水晶発振子は144MHzの昔のトランシーバーの水晶を利用(14MHz台)

この水晶発振子の2倍の周波数をVXOより取り出します。

詳細は回路図を見て頂くとして、29.7MHzから29.8MHzの100kHzを安定して得ることが出来ることを目的とします。

1.まず、IFT1迄を組み立てます、IFTは7kボビンを使用して巻きます。ディップメーターで29MHzに同調させておきます。2個用意します。

2.水晶発振回路を基本波発振器として動作させます。(水晶とコイルの接点をアースに落とす) 14MHz台の周波数になっているか周波数カウンタにて確認しておくと安心です。ここで発振しないと、VXOは無理です。

3.水晶発振回路としての動作を確認後、水晶とコイルの接点をアースから外しVXOとして動作させます。発振しない時は、C2とC3の比を変更してみます。VXO動作にすると、発振強度は弱くなります。

4.VXOとして動作したら、周波数の可変範囲の確認をします、29.7MHzから29.8MHzの100kHzに上下に少し余裕(5~10kHz)があるようにします。可変範囲が狭いときはL1の巻数を少し増やし広すぎるときは減らします、ただ1回の巻数の変更でも発振周波数幅は大きく変わってきますので注意が必要です。

私は少し多めに巻いておいて、少しずつほどいています。

巻数が決定したら、高周波ワニスなどでコイルを固定します。(2004/8/24)現在まだ固定してませんHi)

5.次にIFT4を取り付け配線します。IFT4の2次側に50Ωの抵抗と高周波検出器など(ダイオードとテスターでも可)を接続し、IFT1とIFT4を微調整して出力を最大にします。

6.ここで、オシロスコープを利用できる人は、波形を観測してみましょう。きれいなサインウェーブが見えると思います。出力電圧は、約1Vp-p (50Ω負荷時)有れば良い。

7.次は、C22以降の回路を組み立てます。(広帯域増幅回路です。)

8.T2のコイルは、バイファイラ巻(2本の線を捩じって巻く)にする。結線にはくれぐれも注意する事(間違いやすい)

9.この回路は、入出力インピーダンス50Ω、ゲイン9dBのアンプです。配線に間違いなければ、うまく動作するはず。

10.出力にmWパワー計を接続して、出力を確認します、10~20mW(+10dBm~+13dBm)出ていればOKです。

11.オシロスコープにて波形を観測して、異常発振など無いことを確認しておくと、安心です。

次はVCOです